# SATHYABAMA UNIVERSITY FACULTY OF ELECTRICAL AND ELECTRONICS SEC1201 MICROPROCESSORS AND MICROCONTROLLERS

#### **COURSE MATERIAL**

#### UNIT 1 INTRODUCTION TO MICROPROCESSORS

Introduction, 8085 Architecture, Pin Diagram and signals, Addressing Modes, Timing Diagram-Memory read, Memory write, I/O cycle, Interrupts and its types, Introduction to 8086 microprocessors and its operation.

#### MICROPROCESSORS

Microcomputer System – 8085 Architecture – 8085 Pin Diagram – Buses and Memory Operations – Addressing Modes, Basic concepts of microprocessor programming – Mnemonics – Hex code – fundamentals of assembly language - Instruction set for 8085.

#### **Basic Concepts of Microprocessors**

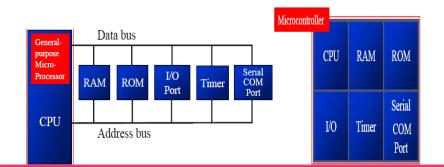

Differences between: Microcomputer, Microprocessor and Microcontroller

- Microcomputer is a computer with a microprocessor as its CPU. Includes memory, I/O etc.

- Microprocessor is a silicon chip which includes ALU, register circuits & control circuits

- Microcontroller is a silicon chip which includes microprocessor, memory & I/O in a single package.

#### What is micro?

Micro is a new addition.

□ In the late 1960's, processors were built using discrete elements.

These devices performed the required operation, but were too large and too slow.

□ It went directly from discrete elements to a single chip. However, comparing today's microprocessors to the ones built in the early 1970's you find an extreme increase in the amount of integration.

#### What is a microprocessor?

- The word comes from the combination of micro and processor.

- Processor means a device that processes whatever. In this context processor means a device that processes numbers, specifically binary numbers, 0's and 1's.

- To process means to manipulate. It is a general term that describes all manipulation. Again in this content, it means to perform certain operations on the numbers that depend on the microprocessor's design. It is a programmable device that takes in numbers, performs on them arithmetic or logical operations according to the program stored in memory and then produces other numbers

As a Programmable device:

- The microprocessor can perform different sets of operations on the data it receives depending on the sequence of instructions supplied in the given program.

- By changing the program, the microprocessor manipulates the data in different ways as Instructions, Words, Bytes, etc.

- They processed information 8-bits at a time. That's why they are called —8-bit processors. They can handle large numbers, but in order to process these numbers, they broke them into 8-bit pieces and processed each group of 8-bits separately.

## What is memory?

- Memory is the location where information is kept while not in current use. It is stored in memory

- Memory is a collection of storage devices. Usually, each storage device holds one bit.

Also, in most kinds of memory, these storage devices are grouped into groups of 8.

These 8 storage locations can only be accessed together. So, one can only read or write in terms of bytes to and form memory.

- Memory is usually measured by the number of bytes it can hold. It is measured in Kilos, Megas and lately Gigas. A Kilo in computer language is 210 =1024. So, a KB (KiloByte) is 1024 bytes. Mega is 1024 Kilos and Giga is 1024 Mega.

- When a program is entered into a computer, it is stored in memory. Then as the microprocessor starts to execute the instructions, it brings the instructions from memory one at a time.

- Memory is also used to hold the data.

- The microprocessor reads (brings in) the data from memory when it needs it and writes (stores) the results into memory when it is done.

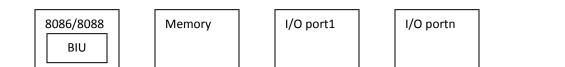

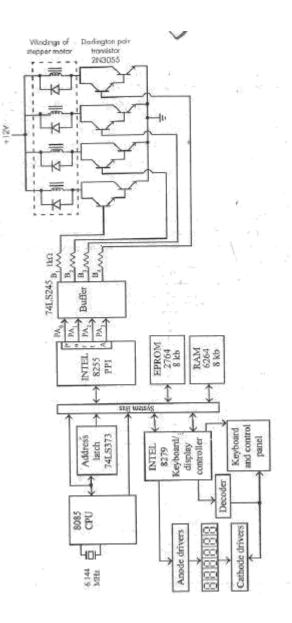

## A MICROPROCESSOR-BASED SYSTEM

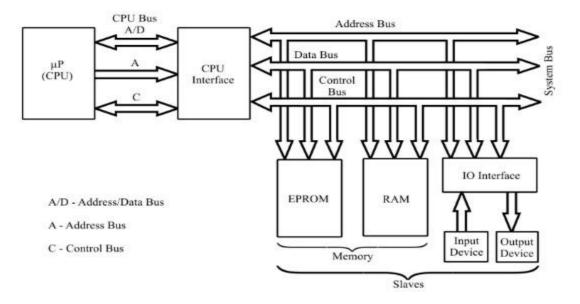

From the above description, we can draw the following block diagram to represent a microprocessor-based system as shown in fig 1

Fig.1. Microprocessor based system (organization of microcomputer)

In this system, the microprocessor is the master and all other peripherals are slaves. The master controls all peripherals and initiates all operations. The buses are group of lines that carry data, address or control signals. The CPU interface is provided to demultiplex the multiplexed lines, to generate the chip select signals and additional control signals. The system bus has separate lines for each signal.

All the slaves in the system are connected to the same system bus. At any time instant communication takes place between the master and one of the slaves. All the slaves have tristate logic and hence normally remain in high impedance state. The processor selects a

slave by sending an address. When a slave is selected, it comes to the normal logic and communicates with the processor.

The EPROM memory is used to store permanent programs and data. The RAM memory is used to store temporary programs and data. The input device is used to enter program, data and to operate system. The output device is also used for examining the results. Since the speed of IO devices does not match with speed of microprocessor, an interface device is provided between system bus and IO device.

## CENTRAL PROCESSING UNIT:

The CPU consists of ALU (Arithmetic and Logic Unit), Register unit and control unit. The CPU retrieves stored instructions and data word from memory; it also deposits processed data in memory.

a) ALU (Arithmetic and Logic Unit)

This section performs computing functions on data. These functions are arithmetic operations such as additions subtraction and logical operation such as AND, OR rotate etc. Result are stored either in registers or in memory or sent to output devices. b) REGISTER UNIT:

It contains various register. The registers are used primarily to store data temporarily during the execution of a program. Some of the registers are accessible to the uses through instructions.

## c) CONTROL UNIT:

It provides necessary timing & control signals necessary to all the operations in the microcomputer. It controls the flow of data between the p and peripherals (input, output & memory). The control unit gets a clock which determines the speed of the p.

The CPU has three basic functions

- It fetches an instructions word stored in memory.

- It determines what the instruction is telling it to do.(decodes the instruction)

- It executes the instruction. Executing the instruction may include some of the following major tasks.

- o Transfer of data from reg. to reg. in the CPU itself.

- o Transfer of data between a CPU reg. & specified memory location.

- o Performing arithmetic and logical operations on data from a specific memory location or a designated CPU register.

- o Directing the CPU to change a sequence of fetching instruction, if processing the data created a specific condition.

- o Performing housekeeping function within the CPU itself inorder to establish desired condition at certain registers.

- o It looks for control signal such as interrupts and provides appropriate responses.

- o It provides states, control, and timing signals that the memory and input/output section can use.

There are three buses:

#### Address Bus:

It is a group of wires or lines that are used to transfer the addresses of Memory or I/O devices. It is unidirectional. In Intel 8085 microprocessor, Address bus was of 16 bits. This means that Microprocessor 8085 can transfer maximum 16 bit address which means it can address 65,536 different memory locations. This bus is multiplexed with 8 bit data bus. So the most significant bits (MSB) of address goes through Address bus (A7-A0) and LSB goes through multiplexed data bus (AD0-AD7).

#### Data Bus:

Data Bus is used to transfer data within Microprocessor and Memory/Input or Output devices. It is bidirectional as Microprocessor requires to send or receive data. The data bus also works as address bus when multiplexed with lower order address bus. Data bus is 8 Bits long. The word length of a processor depends on data bus, thats why Intel 8085 is called 8 bit Microprocessor because it have an 8 bit data bus.

#### Control Bus:

Microprocessor uses control bus to process data that is what to do with the selected memory location. Some control signals are Read, Write and Opcode fetch etc. Various operations are performed by microprocessor with the help of control bus. This is a dedicated bus, because all timing signals are generated according to control signal. The microprocessor is the master, which controls all the activities of the system. To perform a specific job or task, the microprocessor has to execute a program stored in memory. The program consists of a set of

instructions stored in consecutive memory location. In order to execute the program the microprocessor issues address and control signals, to fetch the instruction and data from memory one by one. After fetching each instruction it decodes the instruction and carries out the task specified by the instruction.

#### Memory

To execute a program:

- □ The user enters its instructions in binary format into the memory.

- The microprocessor then reads these instructions and whatever data is needed from memory, executes the instructions and places the results either in memory or produces it on an output device.

#### The three cycle instruction execution model

- □ To execute a program, the microprocessor —readsII each instruction from memory, —interpretsII it, then —executesII it.

- □ To use the right names for the cycles

- □ The microprocessor fetches each instruction, decodes it, and then executes it. This sequence is continued until all instructions are performed.

#### The 8085 Machine Language

The 8085 (from Intel) is an 8-bit microprocessor. The 8085 uses a total of 246 bit patterns to form its instruction set. These 246 patterns represent only 74 instructions. The reason for the difference is that some (actually most) instructions have multiple different formats. Because it is very difficult to enter the bit patterns correctly, they are usually entered in hexadecimal instead of binary.

For example, the combination 0011 1100 which translates into —increment the number in the register called the accumulatorll, is usually entered as 3C.

#### Assembly Language

Entering the instructions using hexadecimal is quite easier than entering the binary combinations. However, it still is difficult to understand what a program written in hexadecimal does. So, each company defines a symbolic code for the instructions.

These codes are called —mnemonicsll.

The mnemonic for each instruction is usually a group of letters that suggest the operation performed.

• Using the same example from before,

00111100 translates to 3C in hexadecimal (OPCODE)

Its mnemonic is: —INR All.

INR stands for —increment registerll and A is short for accumulator.

It is important to remember that a machine language and its associated assembly language are completely machine dependent. In other words, they are not transferable from one microprocessor to a different one.

## Assembling" The Program

How does assembly language get translated into machine language?

- There are two ways:

- 1st there is —hand assembly .

- The programmer translates each assembly language instruction into its equivalent hexadecimal code (machine language). Then the hexadecimal code is entered into memory.

- The other possibility is a program called an —assemblerll, which does the translation automatically.

## 8085 MICROPROCESSOR ARCHITECTURE

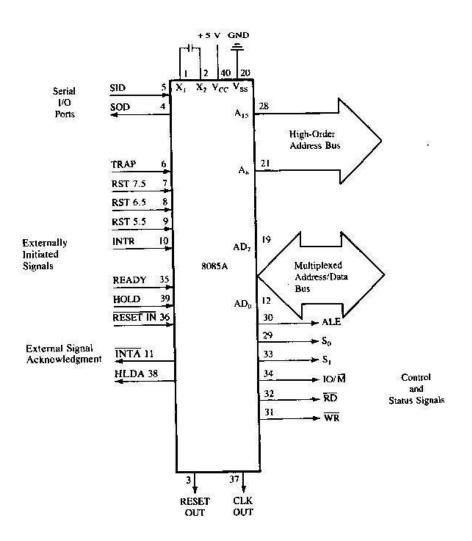

Features of 8085

• 8-bit general purpose µp

- Capable of addressing 64 k of memory

- Has 40 pins as shown in fig 2

- Requires +5 v power supply

- Can operate with 3 MHz clock

- 8085 upward compatible

| X <sub>1</sub>  | 1  | 40 | U VCC             |

|-----------------|----|----|-------------------|

| X, [            | 2  | 39 | HOLD              |

| RST OUT         | 3  | 38 | - HLDA            |

| SOD [           | 4  | 37 | CLK OUT           |

| SID 🗆           | 5  | 36 | RST IN            |

| TRAP            | 6  | 35 | READY             |

| RST7.5          | 7  | 34 | IO/M              |

| RST6.5          | 8  | 33 | □ S <sub>1</sub>  |

| RST5.5          | 9  | 32 | RD RD             |

| INTR [          | 10 | 31 | WR                |

| INTA [          | 11 | 30 | ALE               |

| AD <sub>o</sub> | 12 | 29 | S.                |

| AD <sub>1</sub> | 13 | 28 | □ A <sub>15</sub> |

| AD <sub>2</sub> | 14 | 27 | A14               |

| AD <sub>3</sub> | 15 | 26 | - A13             |

| AD,             | 16 | 25 | □ A <sub>12</sub> |

| AD,             | 17 | 24 | A <sub>11</sub>   |

| AD <sub>6</sub> | 18 | 23 | - A10             |

| AD,             | 19 | 22 | □ A,              |

| GND [           | 20 | 21 |                   |

Pin Diagram of 8085

Fig .2 Pin Diagram of 8085

A8 - A15 (Output 3 State)

Address Bus:The most significant 8 bits of the memory address or the 8 bits of the I/0 address,3 stated during Hold and Halt modes.

AD0 - AD7 (Input/Output 3state)

Multiplexed Address/Data Bus; Lower 8 bits of the memory address (or I/0 address) appear on the bus during the first clock cycle of a machine state. It then becomes the

data bus during the second and third clock cycles. 3 stated during Hold and Halt modes.

ALE (Output) Address Latch Enable

It occurs during the first clock cycle of a machine state and enables the address to get latched into the on chip latch of peripherals. The falling edge of ALE is set to guarantee setup and hold times for the address information. ALE can also be used to strobe the status information. ALE is never 3stated.

#### SO, S1 (Output)

Data Bus Status. Encoded status of the bus cycle: S1 S0 0 0 HALT 0 1 WRITE 1 0 READ 1 1 FETCH S1 can be used as an advanced R/W status.

#### RD (Output 3state)

READ: indicates the selected memory or 1/0 device is to be read and that the Data Bus is available for the data transfer.

#### WR (Output 3state)

WRITE: Indicates the data on the Data Bus is to be written into the selected memory or 1/0 location. Data is set up at the trailing edge of WR. 3 stated during Hold and Halt modes.

## READY (Input)

If Ready is high during a read or write cycle, it indicates that the memory or peripheral is ready to send or receive data. If Ready is low, the CPU will wait for Ready to go high before completing the read or write cycle.

## HOLD (Input)

It indicates that another Master is requesting the use of the Address and Data Buses. The CPU, upon receiving the Hold request will relinquish the use of buses as soon as the completion of the current machine cycle. Internal processing can continue.

The processor can regain the buses only after the Hold is removed. When the Hold is acknowledged, the Address, Data, RD, WR, and IO/M lines are stated.

## HLDA (Output)

HOLD ACKNOWLEDGE indicates that the CPU has received the Hold request and that it will relinquish the buses in the next clock cycle. HLDA goes low after the Hold request is removed. The CPU takes the buses one half clock cycle after HLDA goes low.

## INTR (Input)

INTERRUPT REQUEST is used as a general purpose interrupt. It is sampled only during the next to the last clock cycle of the instruction. If it is active, the Program Counter (PC) will be inhibited from incrementing and an INTA will be issued. During this cycle a RESTART or CALL instruction can be inserted to jump to the interrupt service routine. The INTR is enabled and disabled by software. It is disabled by Reset and immediately after an interrupt is accepted.

## INTA (Output)

INTERRUPT ACKNOWLEDGE: is used instead of (and has the same timing as) RD during the Instruction cycle after an INTR is accepted. It can be used to activate the 8259 Interrupt chip or some other interrupt port.

RESTART INTERRUPTS: These three inputs have the same timing as INTR except they cause an internal RESTART to be automatically inserted. RST 7.5 ~~ Highest Priority RST 6.5 RST 5.5 Lowest Priority

## TRAP (Input)

Trap interrupt is a nonmaskable restart interrupt. It is recognized at the same time as INTR. It is unaffected by any mask or Interrupt Enable. It has the highest priority of any interrupt.

## RESET IN (Input)

Reset sets the Program Counter to zero and resets the Interrupt Enable and HLDA flipflops. None of the other flags or registers (except the instruction register) are affected The CPU is held in the reset condition as long as Reset is applied.

#### RESET OUT (Output)

Indicates CPU is being reset also used as a system RESET. The signal is synchronized to the processor clock.

X1, X2 (Input)

Crystal or R/C network connections to set the internal clock generator X1 can also be an external clock input instead of a crystal. The input frequency is divided by 2 to give the internal operating frequency.

CLK (Output)

Clock Output for use as a system clock when a crystal or R/ C network is used as an input to the CPU. The period of CLK is twice the X1, X2 input period.

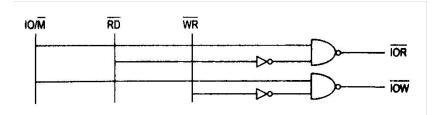

IO/M (Output)

IO/M indicates whether the Read/Write is to memory or I/O Tristated during Hold and Halt modes.

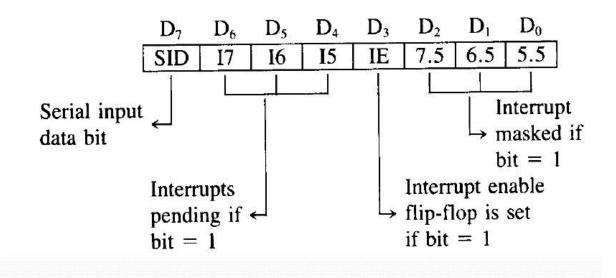

SID (Input)

Serial input data line The data on this line is loaded into accumulator bit 7 whenever a RIM instruction is executed.

SOD (output)

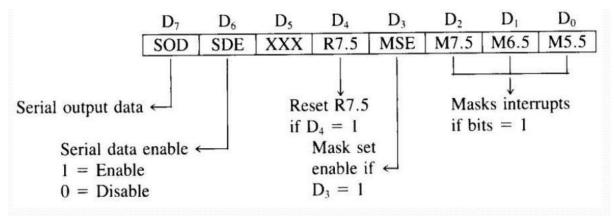

Serial output data line. The output SOD is set or reset as specified by the SIM instruction.

Vcc +5 volt supply.

Vss Ground Reference.

## Signal Classification of 8085

The signal Classification of 8085 is as shown in fig3.

Fig: 3 Signal Classifications of 8085

System Bus - wires connecting memory & I/O to microprocessor

## - ADDRESS BUS

Unidirectional

□ Identifying peripheral or memory location

– DATA BUS

- □ Bidirectional

- □ Transferring data

## - CONTROL BUS

- □ Synchronization signals

- □ Timing signals

- □ Control signal

## ARCHITECTURE OF INTEL 8085 MICROPROCESSOR

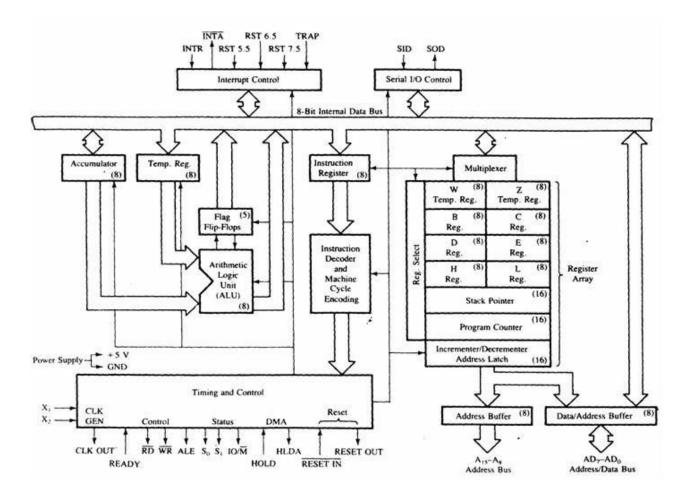

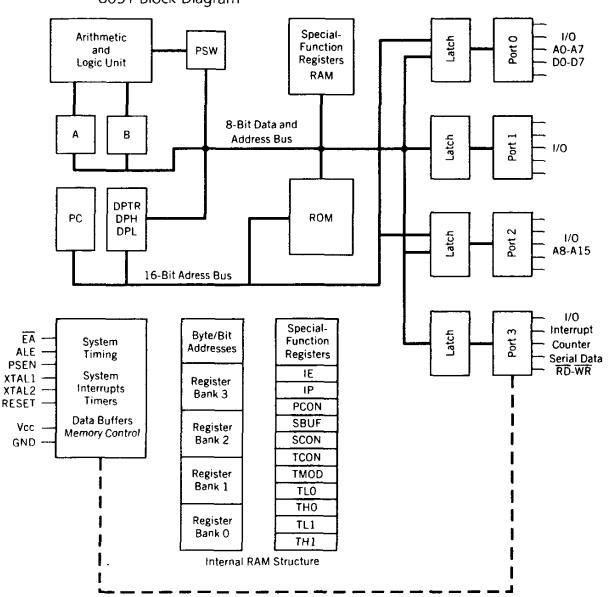

Fig:4 Architecture of intel 8085 microprocessor

The architecture of INTEL 8085 microprocessor is as shown in fig4.

## Intel 8085 Microprocessor

Microprocessor consists of:

- Control unit: control microprocessor operations.

- ALU: performs data processing function.

- Registers: provide storage internal to CPU.

- Interrupts

Internal data bus

# The ALU

• In addition to the arithmetic & logic circuits, the ALU includes the accumulator, which is part of every arithmetic & logic operation.

• Also, the ALU includes a temporary register used for holding data temporarily during the execution of the operation. This temporary register is not accessible by the programmer.

# Registers

**General Purpose Registers**

B, C, D, E, H & L (8 bit registers)

- Can be used singly

- Or can be used as 16 bit register pairs

BC, DE, HL

□ H & L can be used as a data pointer (holds memory address)

□ Special Purpose Registers

□ Accumulator (8 bit register)

- □ Store 8 bit data

- □ Store the result of an operation

- □ Store 8 bit data during I/O transfer Address

## **Flag Register**

- 8 bit register shows the status of the microprocessor before/after an operation

- S (sign flag), Z (zero flag), AC (auxillary carry flag), P (parity flag) & CY (carry flag)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| S  | Z  | Х  | AC | Х  | Р  | Х  | CY |

# Sign Flag

- Used for indicating the sign of the data in the accumulator

- The sign flag is set if negative (1 negative)

- The sign flag is reset if positive (0 –positive)

## Zero Flag

- Is set if result obtained after an operation is 0

- Is set following an increment or decrement operation of that register

## Carry Flag

10110011

+ 01001101

\_\_\_\_\_

0000000

- Is set if there is a carry or borrow from arithmetic operation

\_\_\_\_\_

1011 0101 1011 0101

+ 0110 1100 - 1100 1100

\_\_\_\_\_

Carry 1 0010 0001 Borrow 1 1110 1001

## Auxillary Carry Flag

- Is set if there is a carry out of bit 3

## **Parity Flag**

- Is set if parity is even

- Is cleared if parity is odd

## **The Internal Architecture**

We have already discussed the general purpose registers, the Accumulator, and the flags.

## The Program Counter (PC)

- This is a register that is used to control the sequencing of the execution of instructions.

- This register always holds the address of the next instruction.

- Since it holds an address, it must be 16 bits wide.

#### The Stack pointer

- The stack pointer is also a 16-bit register that is used to point into memory.

- The memory this register points to is a special area called the stack.

- The stack is an area of memory used to hold data that will be retreived soon.

- The stack is usually accessed in a Last In First Out (LIFO) fashion.

#### Non Programmable Registers

Instruction Register & Decoder

- Instruction is stored in IR after fetched by processor

- Decoder decodes instruction in IR

#### Internal Clock generator

- 3.125 MHz internally

- 6.25 MHz externally

#### The Address and Data Busses

•The address bus has 8 signal lines A8 – A15 which are unidirectional.

•The other 8 address bits are multiplexed (time shared) with the 8 data bits.

So, the bits AD0 – AD7 are bi-directional and serve as A0 – A7 and D0 – D7 at the same time.

•During the execution of the instruction, these lines carry the address bits during the early part, then during the late parts of the execution, they carry the 8 data bits.

In order to separate the address from the data, we can use a latch to save the value before the function of the bits changes.

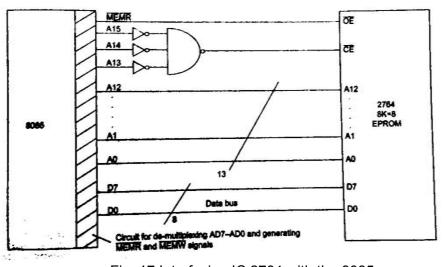

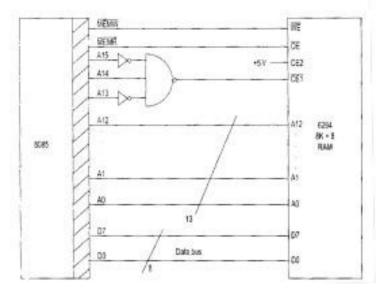

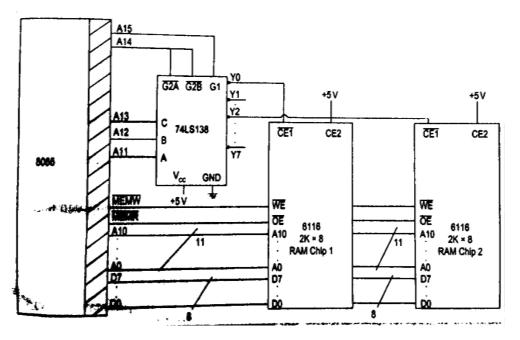

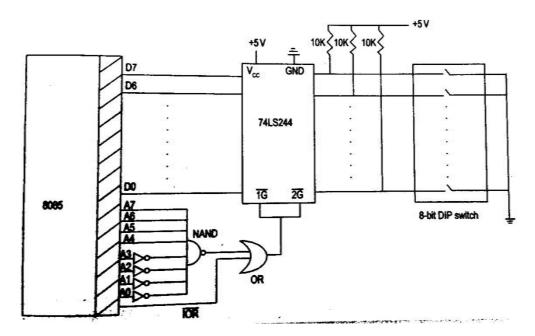

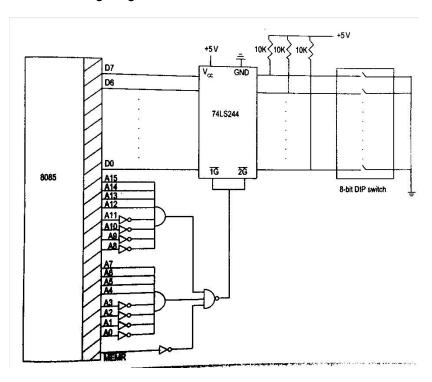

## **Demultiplexing AD7-AD0**

– From the above description, it becomes obvious that the AD7– AD0 lines are serving a dual purpose and that they need to be demultiplexed to get all the information. – The high order bits of the address remain on the bus for three clock periods. However, the low order bits remain for only one clock period and they would be lost if they are not saved externally. Also, notice that the low order bits of the address disappear when they are needed most.

– To make sure we have the entire address for the full three clock cycles, we will use an external latch to save the value of AD7– AD0 when it is carrying the address bits. We use the ALE signal to enable this latch.

## Demultiplexing AD7-AD0

Given that ALE operates as a pulse during T1, we will be able to latch the address. Then when ALE goes low, the address is saved and the AD7– AD0 lines can be used for their purpose as the bi-directional data lines.

## Demultiplexing the Bus AD7 – AD0

- The high order address is placed on the address bus and hold for 3 clk periods,

- The low order address is lost after the first clk period, this address needs to be hold however we need to use latch

- The address AD7 AD0 is connected as inputs to the latch 74LS373.

- The ALE signal is connected to the enable (G) pin of the latch and the OC Output control of the latch is grounded

## ADDRESSING MODES

The microprocessor has different ways of specifying the data for the instruction. These are called —addressing modes.

The 8085 has four addressing modes:

- Implied CMA

- Immediate MVI B, 45

– Direct LDA 4000

– Indirect LDAX B

Load the accumulator with the contents of the memory location whose address is stored in the register pair BC).

Many instructions require two operands for execution. For example transfer of data between two registers. The method of identifying the operands position by the instruction format is known as the addressing mode. When two operands are involved in an instruction, the first operand is assumed to be in a register Mp itself.

Types of Addressing Modes

- Register addressing

- Direct addressing mode

- Register indirect addressing

- Immediate Addressing mode

- Implied addressing mode

# Register Addressing

This type of addressing mode specifies register or register pair that contains data.ie (only the register need be specified as the address of the operands).

Example MOV B, A (the content of A is copied into the register B)

# Direct Addressing Mode

Data is directly copied from the given address to the register.

Example LDA 3000H (The content at the location 3000H is copied to the register A).

# **Register Indirect Addressing**

In this mode, the address of operand is specified by a register pair

Example MOV A, M (Move data from memory location specified by H-L pair to accumulator)

Immediate Addressing Mode

In this mode, the operand is specified within the instruction itself.

Example MVI A, 05 H (Move 05 H in accumulator.)

Implied Addressing Mode

This mode doesn't require any operand. The data is specified by opcode itself.

Example RAL,

CMP

## TIMING DIAGRAM

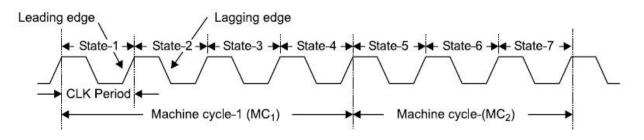

Timing diagram is the display of initiation of read/write and transfer of data operations under the control of 3-status signals IO / M, S1, and S0. All actions in the microprocessor are controlled by either leading or trailing edge of the clock.

Machine Cycle

It is the time required by the microprocessor to complete the operation of accessing the memory devices or I/O devices. In machine cycle various operations like opcode fetch, memory read, memory write, I/O read, I/O write are performed.

T-State

Each clock cycle is called as T-states.

Each machine cycle is composed of many clock cycles. Since, the data and instructions, both are stored in the memory, the  $\mu$ P performs fetch operation to read the instruction or data and then execute the instruction. The 3-status signals: IO / M, S1, and S0 are generated at the beginning of each machine cycle. The unique combination of these 3-status signals identify read or write operation and remain valid for the duration of the cycle.

|                            |        | Status         |                |    | Controls |      |

|----------------------------|--------|----------------|----------------|----|----------|------|

| Machine cycle              | IO / M | S <sub>1</sub> | S <sub>0</sub> | RD | WR       | INTA |

| Opcode Fetch (OF)          | 0      | 1              | 1              | 0  | 1        | 1    |

| Memory Read                | 0      | 1              | 0              | 0  | 1        | 1    |

| Memory Write               | 0      | 0              | 1              | 1  | 0        | 1    |

| I/O Read (I/OR)            | 1      | 1              | 0              | 0  | 1        | 1    |

| I/O Write (I/OW)           | 1      | 0              | 1              | 1  | 0        | 1    |

| Acknowledge of INTR (INTA) | 1      | 1              | 1              | 1  | 1        | 0    |

| BUS Idle (BI) : DAD        | 0      | 1              | 0              | 1  | 1        | 1    |

| ACK of RST, TRAP           | 1      | 1              | 1              | 1  | 1        | 1    |

| HALT                       | Z      | 0              | 0              | Z  | Z        | 1    |

| HOLD                       | Z      | X              | X              | Z  | Z        | 1    |

Table 1 Machine Cycle Status And Control Signals

$X \Rightarrow$  Unspecified, and  $Z \Rightarrow$  High impedance state

Table1 shows details of the unique combination of these status signals to identify different machine cycles. Thus, time taken by any  $\mu$ P to execute one instruction is calculated in terms of the clock period. The execution of instruction always requires read and writes operations to transfer data to or from the  $\mu$ P and memory or I/O devices. Each read/ write operation constitutes one machine cycle (MC1) as indicated in Fig.7. Each machine cycle consists of many clock periods/ cycles, called T-states.

Fig.7 Machine cycle showing clock periods

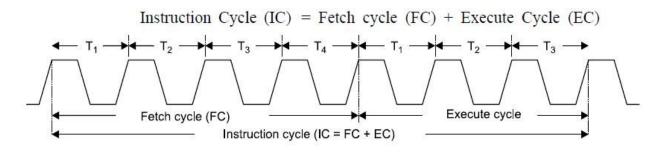

Processor Cycle:

The functions of the microprocessor are divided into fetch and execute cycle of any instruction of a program. The program is nothing but number of instructions stored in the memory in sequence. In the normal process of operation, the microprocessor fetches (receives or reads) and executes one instruction at a time in the sequence until it executes the halt (HLT) instruction.

Instruction Cycle

An instruction cycle is defined as the time required to fetch and execute an instruction. For executing any program, basically 2-steps are followed sequentially with the help of clocks

- Fetch, and

- Execute.

The time taken by the  $\mu$ P in performing the fetch and execute operations are called fetch and execute cycle. Thus, sum of the fetch and execute cycle is called the instruction cycle as indicated in Fig. 8. Each read or writes operation constitutes a machine cycle. The instructions of 8085 require 1–5 machine cycles containing 3–6 states (clocks). The 1st machine cycle of any instruction is always an Op Code fetch cycle in which the processor decides the nature of instruction. It is of at least 4-states. It may go up to 6-states.

# Rules To Identify Number Of Machine Cycles In An Instruction:

- If an addressing mode is direct, immediate or implicit then No. of machine cycles = No. of bytes.

- If the addressing mode is indirect then No. of machine cycles = No. of bytes + 1. Add +1 to the No. of machine cycles if it is memory read/write operation.

- If the operand is 8-bit or 16-bit address then, No. of machine cycles = No. of bytes +1.

- These rules are applicable to 80% of the instructions of 8085.

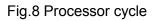

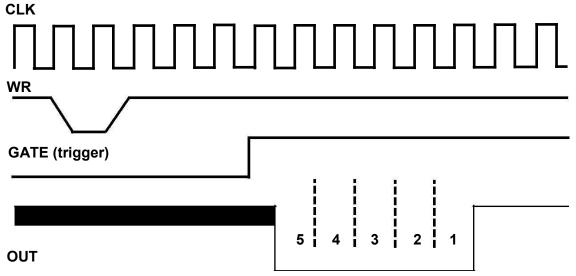

Timing Diagram of Opcode Fetch

The process of Opcode fetch operation requires minimum 4-clock cycles T1, T2, T3, and T4 and is the 1st machine cycle (M1) of every instruction.

# Example

Fetch a byte 41H stored at memory location 2105H.

For fetching a byte, the microprocessor must find out the memory location where it is stored. Then provide condition (control) for data flow from memory to the microprocessor. The process of data flow and timing diagram of fetch operation are shown in Fig. 9. The microprocessor fetches Opcode of the instruction from the memory as per the sequence below

- □ A low IO/M means microprocessor wants to communicate with memory.

- □ The microprocessor sends a high on status signal S1 and S0 indicating fetch operation.

- □ The microprocessor sends 16-bit address. AD bus has address in 1st clock of the 1st machine cycle, T1.

- $\Box$  AD7 to AD0 address is latched in the external latch when ALE = 1.

- $\Box$  AD bus now can carry data.

- □ In T2, the RD control signal becomes low to enable the memory for read operation.

- □ The memory places opcode on the AD bus

- □ The data is placed in the data register (DR) and then it is transferred to IR.

- □ During T3 the RD signal becomes high and memory is disabled.

- During T4 the opcode is sent for decoding and decoded in T4.

- □ The execution is also completed in T4 if the instruction is single byte.

- More machine cycles are essential for 2- or 3-byte instructions. The 1st machine cycle M1 is meant for fetching the opcode. The machine cycles M2 and M3 are required either read/ write data or address from the memory or I/O devices.

Fig. 9 Opcode fetch

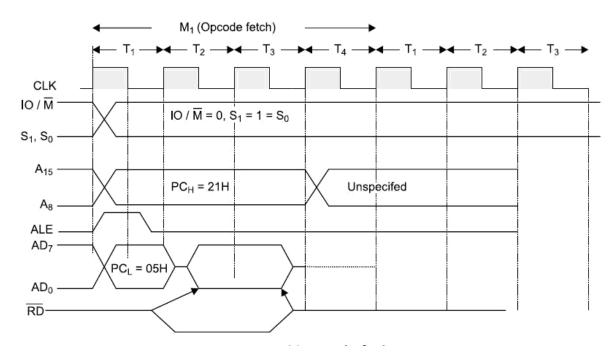

Example For Opcode Fetch

□ Explain the execution of MVI B, 05H stored at locations indicated below

| Mnemonics  | Machine code | Memory Locations |

|------------|--------------|------------------|

| MVI B, 05H | 06H          | 1000H            |

|            | 05H          | 1001H            |

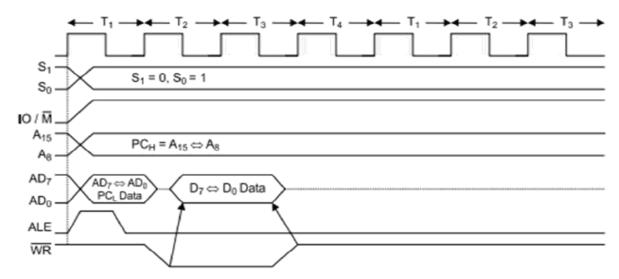

Fig. 10 Timing diagram for MVI B,05H

The MVI B, 05H instruction requires 2-machine cycles (M1 and M2). M1 requires 4states and M2 requires 3-states, total of 7-states as shown in Fig. 10. Status signals IO/M, S1 and S0 specifies the 1st machine cycle as the op-code fetch. In T1-state, the high order address {10H} is placed on the bus A15  $\Leftrightarrow$ A8 and low-order address {00H} on the bus AD7  $\Leftrightarrow$ AD0 and ALE = 1. In T2 -state, the RD line goes low and the data 06 H from memory location 1000H are placed on the data bus. The fetch cycle becomes complete in T3-state. The instruction is decoded in the T4-state. During T4-state, the contents of the bus are unknown. With the change in the status signal, IO/M = 0, S1 = 1 and S0 = 0, the 2nd machine cycle is identified as the memory read. The address is 1001H and the data byte [05H] is fetched via the data bus. Both M1 and M2 perform memory read operation, but the M1 is called op-code fetch i.e., the 1st machine cycle of each instruction is identified as the opcode fetch cycle.

| Mnemonic  | Instruction Byte | Machine Cycle       | T-sstates |

|-----------|------------------|---------------------|-----------|

| MVI B,05H | Opcode           | Opcode Fetch        | 4         |

|           | Immediate Data   | Read Immediate Data | 3         |

|           |                  |                     | 7         |

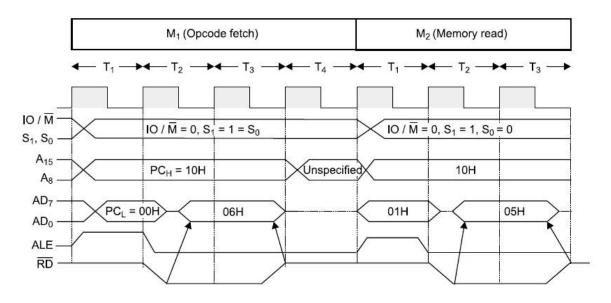

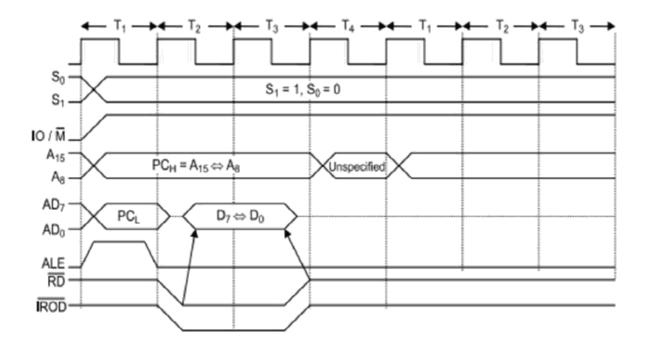

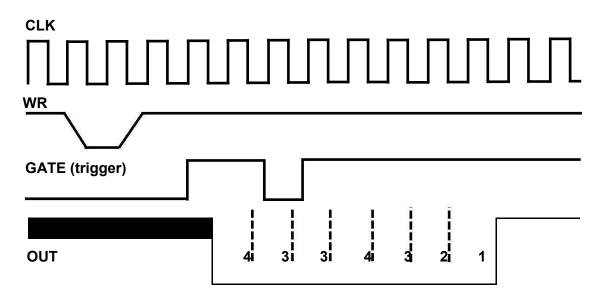

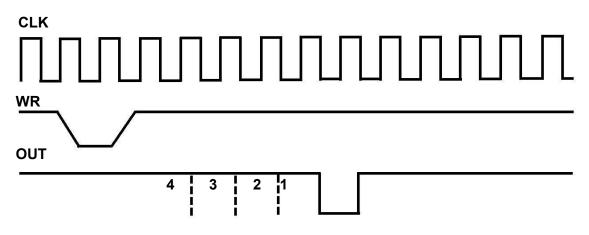

# TIMING DIAGRAM OF MEMORY READ

- $\Box$  It is used to fetch one byte from the memory.

- □ It requires 3 T-States.

- $\Box$  It can be used to fetch operand or data from the memory.

- □ During T1, A8-A15 contains higher byte of address. At the same time ALE is high. Therefore Lower byte of address A0-A7 is selected from AD0-AD7 as shown in fig 11.

- □ Since it is memory ready operation, IO/M (bar) goes low.

- During T2 ALE goes low, RD (bar) goes low. Address is removed from AD0-AD7 and data D0-D7 appears on AD0-AD7.

- During T3, Data remains on AD0-AD7 till RD (bar) is at low signal.

Fig 11.Memory read timing diagram

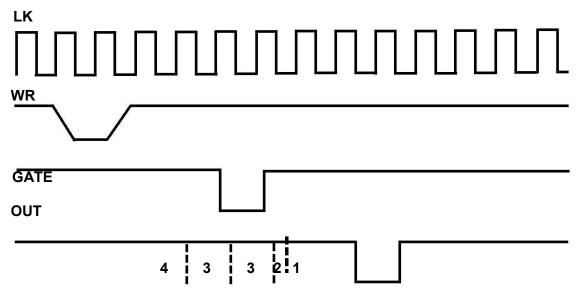

# TIMING DIAGRAM OF MEMORY WRITE

- $\hfill\square$  It is used to send one byte into memory.

- □ It requires 3 T-States.

- □ During T1, ALE is high and contains lower address A0-A7 from AD0-AD7.

- □ A8-A15 contains higher byte of address.

- $\Box$  As it is memory operation, IO/M (bar) goes low.

- □ During T2, ALE goes low, WR (bar) goes low and Address is removed from AD0-AD7 and then data appears on AD0-AD7 as in fig 12.

- □ Data remains on AD0-AD7 till WR (bar) is low.

Fig 12.Memory Write timing diagram

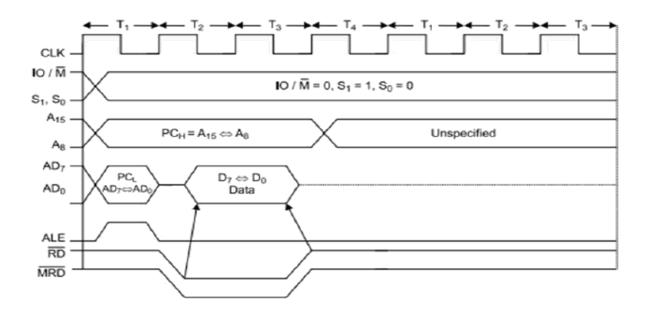

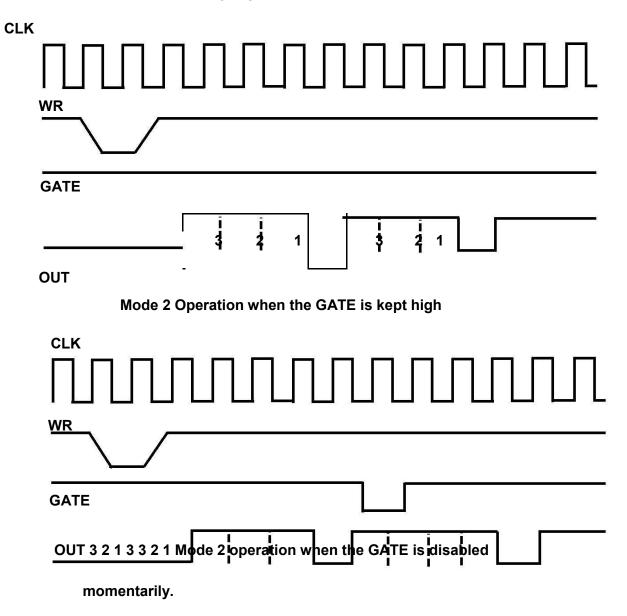

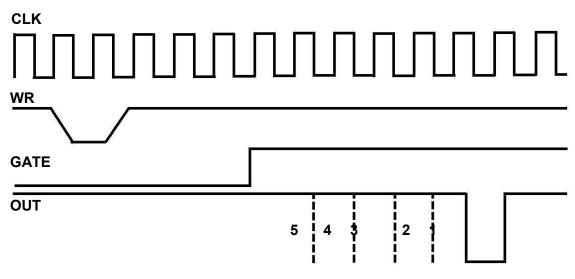

# TIMING DIAGRAM OF IO READ

- $\hfill\square$  It is used to fetch one byte from an IO port.

- □ It requires 3 T-States.

- During T1, The Lower Byte of IO address is duplicated into higher order address bus A8-A15 as in fig13.

- □ ALE is high and AD0-AD7 contains address of IO device.

- $\Box$  IO/M (bar) goes high as it is an IO operation.

- During T2, ALE goes low, RD (bar) goes low and data appears on AD0-AD7 as input from IO device.

- During T3 Data remains on AD0-AD7 till RD (bar) is low.

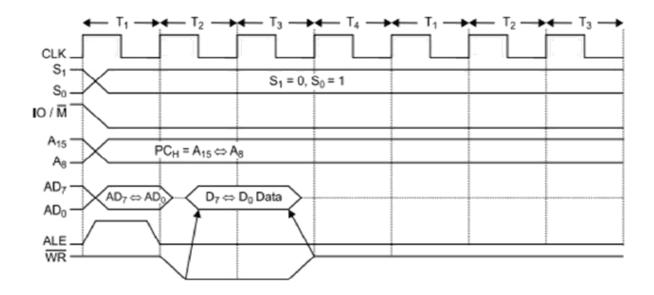

## TIMING DIAGRAM OF IO WRITE

- □ It is used to writ one byte into IO device.

- $\Box$  It requires 3 T-States.

- During T1, the lower byte of address is duplicated into higher order address bus A8-A15 as in fig 14.

- □ ALE is high and A0-A7 address is selected from AD0-AD7.

- $\Box$  As it is an IO operation IO/M (bar) goes low.

- □ During T2, ALE goes low, WR (bar) goes low and data appears on AD0-AD7 to write data into IO device.

- □ During T3, Data remains on AD0-AD7 till WR(bar) is low.

Fig 14. IO Write timing diagram

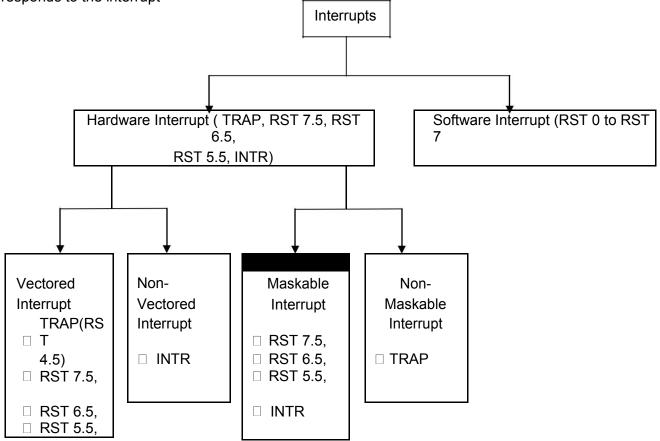

#### **INTERRUPT**:

An interrupt is a signal initiated by an external device to the microprocessor. Once this signal is received, the microprocessor completes the execution of the current instruction and responds to the interrupt

Fig 15. Structured classification of interrupts

#### **SOFTWARE INTERRUPTS OF 8085**

The software interrupts are program instructions. When the instruction is executed, the processor executes an interrupt service routine stored in the vector address of the software interrupt instruction. The software interrupts of 8085 are RST 0, RST 1, RST 2, RST 3, RST 4, RST 5, RST 6 and RST 7.

The vector addresses of software interrupts are given in table below

| Interrupt      | Vector address                         | Interrupt          | Vec |

|----------------|----------------------------------------|--------------------|-----|

| RST 0<br>RST 1 | 0000 <sub>H</sub><br>0008 <sub>H</sub> | RST 7.5<br>RST 6.5 |     |

| RST 2<br>RST 3 | 0010 <sub>H</sub><br>0018 <sub>H</sub> | RST 5.5            |     |

| RST 4<br>RST 5 | 0020 <sub>H</sub><br>0028 <sub>H</sub> | TRAP               | -   |

| RST 6<br>RST 7 | 0030 <sub>H</sub><br>0038 <sub>H</sub> |                    |     |

| Interrupt | Vector address    |

|-----------|-------------------|

| RST 7.5   | 003C <sub>H</sub> |

| RST 6.5   | 0034 <sub>H</sub> |

| RST 5.5   | 002C <sub>H</sub> |

| TRAP      | 0024              |

The software interrupt instructions are included at the appropriate (or required) place in the main program. When the processor encounters the software instruction, it pushes the content of PC (Program Counter) to stack. Then loads the Vector address in PC and starts executing the Interrupt Service Routine (ISR) stored in this vector address. At the end of ISR, a return instruction - RET will be placed. When the RET instruction is executed, the processor POP the content of stack to PC. Hence the processor control returns to the main program after servicing the interrupt. Execution of ISR is referred to as servicing of interrupt. All software interrupts of 8085 are vectored interrupts. The software interrupts cannot be masked and they cannot be disabled. The software interrupts are RST0, RST1, ... RST7 (8 Nos).

#### **HARDWARE INTERRUPTS OF 8085**

These are the interrupts provided as signals to the microprocessor. There are five interrupt signals in 8085. They are Trap, RST 7.5, RST 6.5, RST 5.5 and INTR. The

priority of the interrupts is from TRAP to INTR. The program executed for the service of the interrupting device is called the service routine.

## TRAP

• This interrupt is a Non-Maskable interrupt (NMI). It is unaffected by any mask or interrupt enable.

• TRAP is the highest priority and vectored interrupt(as vector address is fixed i.e. memory location where to transfer control).

• TRAP interrupt is edge and level triggered. This means hat the TRAP must go high and remain high until it is acknowledged.

• In sudden power failure, it executes a ISR and send the data from main memory to backup memory.

• The signal, which overrides the TRAP, is HOLD signal. (i.e., If the processor receives HOLD and TRAP at the same time then HOLD is recognized first and then TRAP is recognized).

• There are two ways to clear TRAP interrupt.

1.By resetting microprocessor (External signal)

2.By giving a high TRAP ACKNOWLEDGE (Internal signal)

## RST 7.5

- The RST 7.5 interrupt is a Maskable interrupt.

- It has the second highest priority.

• It is edge sensitive. i.e. Input goes to high and no need to maintain high state until it recognized.

• Maskable interrupt. It is disabled by,

1.DI instruction

2.System or processor reset.

3.After reorganization of interrupt.

## RST 6.5 and 5.5

• The RST 6.5 and RST 5.5 both are level triggered (i.e.) Input goes to high and stay high until it recognized.

• Maskable interrupt. It is disabled by,

- 1. DI, SIM instruction

- 2. System or processor reset.

- 3. After reorganization of interrupt.

- Enabled by EI instruction.

- The RST 6.5 has the third priority whereas RST 5.5 has the fourth priority.

These interrupts are classified further into two classes based on the destination address and response. Based on the service routine address, interrupts are classified in to vectored and non-vectored interrupt.

## Vectored Interrupt:

If the address of the service routine is known to the microprocessor, i.e. if the service routine begins at a predefined address, then the interrupts are called vectored interrupts. The vectored address is calculated as  $(nx8)_{16}$  where n is the number of RST.

For example:

The vectored address of RST 7.5 is 7.5 x 8=60.0

60 in hexadecimal number system is 003C. Therefore the branching address of RST 7.5 is 003C.

| Interrupt      | Address |

|----------------|---------|

| RST 7.5        | 003C    |

| RST 6.5        | 0034    |

| RST 5.5        | 002C    |

| TRAP (RST 4.5) | 0024    |

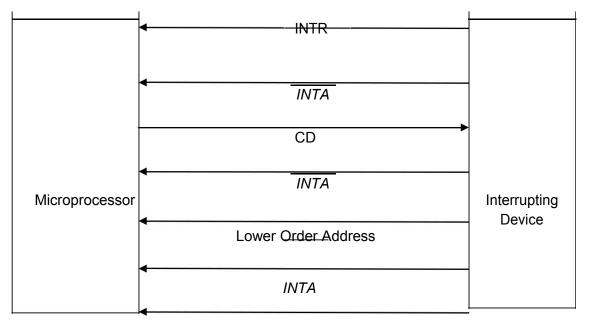

# Non vectored Interrupt:

The address of the service routine is not known in prior to the microprocessor. It is sent by the interrupting device.

Higher Order Address

# Fig 16.Work flow of Non vectored Interrupt

When the interrupt flipflop is enabled and INTR is high, microprocessor executes the current instruction and makes INTA low. The interrupting device sends the service routine address to the microprocessor as shown in fig 16.

Based on the flexibility to enable or disable interrupt, the interrupts are classified as maskable interrupt and non maskable interrupt.

**Maskable Interrupt:** Even if the interrupt signals are high, microprocessor will respond to these signals only when interrupt flip flop is enabled. Example RST 7.5, RST 6.5, RST 5.5, INTR

#### Non-Maskable Interrupt:

Once the signal is enabled, the microprocessor immediately responds to this interrupt. Example: TRAP

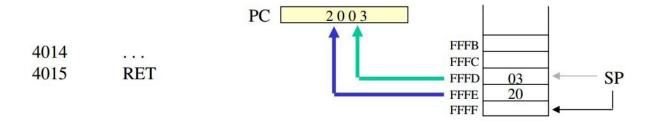

#### STACK

Stack is the upper part of the memory used for storing temporary information. It is a Last In First Out Memory (LIFO) . In 8085, it is accessed using PUSH and POP instructions. During pushing, the stack operates in a —decrement then storell style. The stack pointer is decremented first, then the information is placed on the stack. During poping, the stack operates in a —use then incrementll style. The information is retrieved from the top of the the stack and then the pointer is incremented. The SP pointer always points to —the top of the stackll.

#### Program Status Word (PSW)

The 8085 recognizes one additional register pair called the PSW (Program Status Word). This register pair is made up of the Accumulator and the Flags registers. It is possible to push the PSW onto the stack, do whatever operations are needed, then POP it off of the stack. The result is that the contents of the Accumulator and the status of the Flags are returned to what they were before the operations were executed.

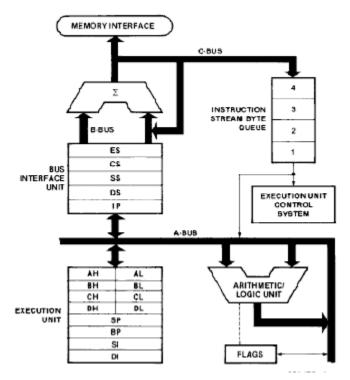

## INTRODUCTION TO INTEL 8086 MICROPROCESSOR Fundamental components of 8086/8088

The 8086/8088 microprocessor consists of four functional units.

- 1) Execution unit (EU): decodes and executes machine instructions.

- 2) Arithmetic and logic unit (ALU): performs math and logical operations on command by the EU.

- 3) Internal storage (sometime called registers): is used for internal data storage.

- 4) Bus interface unit (BIU): handles all communications with the I/O via the system bus and maintains instruction queue.

Block Diagram of 8086 Microprocessor

## **Execution Unit (EU)**

The Execution Unit controls the activity within the processor. It is responsible for retrieving binary machine-language instructions from the **Instruction Queue** maintained by the Bus Interface Unit deciphering them, and seeing to it that the correct steps are performed within the processor to carry out each instruction. If an instruction requires the use of data that is stored internally, in a register, then the Execution Unit retrieves the data from the correct register; if the instruction requires external data, from memory perhaps, then the EU requests the data from the Bus Interface Unit.

Whenever an instruction calls for an arithmetic or logical function, the EU passes the data to Arithmetic and Logic Unit together with a command telling the ALU what to do with the data. The EU then accepts the resulting data from the ALU and sees to it that it is stored into correct location (register or memory), as designated by the instruction.

## Arithmetic and Logic Unit (ALU)

The ALU contains circuitry that is capable to perform arithmetic (+, -, \*, /) operations and logic operations (AND, OR, NOT, XOR) operations. As the ALU completes a requested operation, it also controls individual bits of Flags register (sometimes called the program status register). It sets (1) or clear (0) the correct bits to reflect specific characteristics of the result of the operation, such as whether the result was zero or non-zero, whether it was positive or negative, or if the result is too big to be stored in a byte or word. The EU checks the status of those Flag bits whenever executing conditional jump instructions.

## **Bus Interface Unit (BIU)**

BIU is a circuitry to response memory access and communicate with I/O devices. In most microprocessors, these functions are performed by EU, and some times the EU has to be idle due to different speed and serial execution.

In the design of the 8086/8088, Intel introduces BIU in order to avoid idle time and hold an instruction queue such that instructions can be executed in a pipeline fashion.

#### System Bus and Other Support Hardware Devices in IBM PC

In order to build a complete computer, there are a number of other hardware devices (chips) in the IBM PC. Some of them are:

#### Memory

Up to one megabyte of system memory, including that which is on the system board, the video adapter card, and any add-on memory boards.

#### Timer chip

Generates an external interrupt every fifty-five milliseconds to allow the PC to keep track of real time (system data and time).

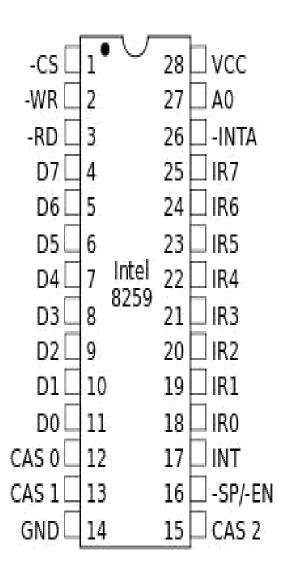

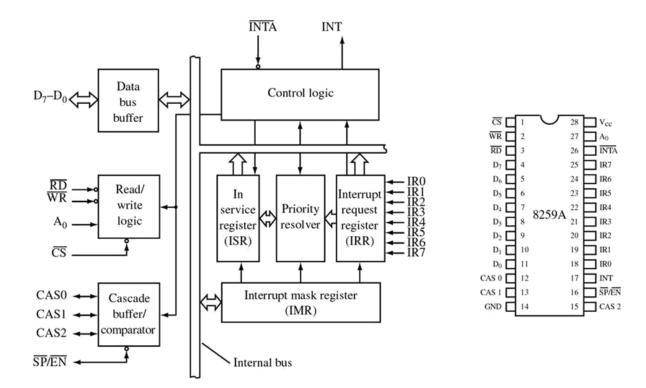

#### 8259 Interrupt Controller chip

Processes hardware (external) interrupts.

#### 6845 CRT Controller

Located on the video adapter card. Controls the video signals to the monitor.

#### NEC D765 or Intel 8272 Floppy Disk Controller

Located on the disk adapter card. Acts as an interface between the processor and the disk drive.

#### Inter 8237 Direct Memory Access (DMA) Controller

Located on the system board. Used by the disk controller to transfer data between disk and memory.

# 8250 Asynchronous Communications Element or Universal Asynchronous Receiver/Transmitter (UART)

Located on each serial communications adapter card (COM1, COM2, etc.).

System Bus: is a series of conductive traces of signal lines on the system board, which is used to communicate between 8086/8088 (cpu) and all other devices.

The system bus is made up of three functional parts:

- 1) Data bus

- Address bus

- 3) Control bus

To read from memory, for example, the Bus Interface Unit puts the correct memory address onto the Address Bus and puts the command to read from memory onto the Control Bus. All devices connected to the bus see this address and command simultaneously, but only the memory-control circuitry respond to it. The memory-control circuitry is then responsible for decoding the address, retrieving the data from the appropriate memory chips, and placing the data onto the Data Bus for retrieval by the BIU.

To write to memory, the BIU puts the memory address onto the Address Bus, the byte of data onto the Data Bus, and a command to write data onto memory of the control bus. The memory-control circuitry decodes the command and the address, retrieves the data from the Data Bus, and stores it into the correct memory chips. All other circuitry simply ignores the command.

Communication with the many special-purpose microprocessors attached to the System Bus is accomplished through I/O ports. I/O ports are used for the transfer of data between the 8086/8088 processor and the other support hardware within the system. The In and OUT instructions tell the processor to input or output data through the I/O ports.

When executing an IN instruction, the BIU puts the I/O port address onto the Address Bus and puts the command to input data onto the Control Bus. The circuitry on some peripheral device attacked to the bus recognizes the red command and decodes the I/O port as the address of some register within the peripheral device. It then retrieves the data from the register and places it onto the Data Bus from which it is retrieved by the BIU and fed to the Execution Unit within the processor.

To execute an OUT instruction, the BIU puts the command to output data onto the Control Bus, and I/O address onto the Address Bus, and the data to be output onto the Data Bus. The circuitry of a peripheral device is then responsible for recognizing the output command and the I/O address and for retrieving the data from the data bus.

#### Memory and Internal Storage

#### **Storage Elements**

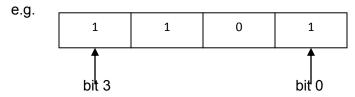

- Bits: The smallest storage element on any computer is the bit, which can have a value of 0 or 1.

- Nibbles: A nibble is a sequence of 4 bits.

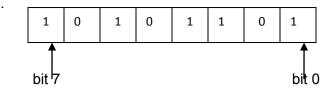

• Bytes: A byte is a sequence of 8 bits.

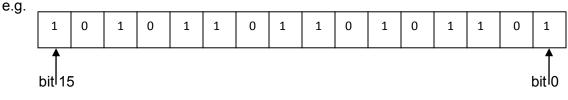

e.g.

• Words: in 8086/8088, a word consists of 16 bits that can be viewed as:

2) A vertical sequence of 2 bytes e.g..

- Note: in memory, the least significant bye (bits 0-7) is stored in lower numbered memory location, and the most significant byte (bits 8-15) is stored in the next higher numbered location.

- Double words: Two words represents a double word which is viewed as

- 1) A horizontal sequence of 32 bits or

- 2) A vertical sequence of 2 words or

- 3) A vertical sequence of 4 bytes

Note: in memory, its 0-7 bits would come first; bits 8-15 would be in the next higher numbered byte and so on.

- Quadword: A quadword is 2 double words, hence 4 words or 8 bytes.

- Tenbytes: A tenbyte is a sequence of 10 bytes.

# Memory

Computer memory consists of an ordered sequence of storage units (8-bits called bytes), each with its own address.

• 8086/8088's memory is bytes-addressable, which means that each byte has its own address, e.g. if A is the address of a word (16 bits), then A is actually the address of

the first byte (bits 0-7) of the word, A+1 is the address of the second byte (bits 8-15) of the word, and A+2 is the address of the next word.

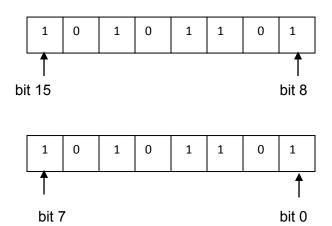

- Memory address space: (MAS): 2<sup>20</sup>= 1,048,576= 1M(bytes) (address space: 0—2<sup>20</sup>-1, i.e.00000-fffff: in hexadecimal)

- Map of the memory address space (MAS)

The whole MAS is organized by a 2<sup>16</sup> \* 2<sup>4</sup> matrix: there are 2<sup>16</sup> paragraphs, each of which with 16 (2<sup>4</sup>) bytes.

Paragraph numbers:

Hexadecimar manuser oy

The hexadecimal number system uses sixteen characters to represent umbers:0 through 9 and A through F; A is worth ten, B is worth eleven, ..., and F is fifteen. In assembly program, the hexadecimal will be indicated by the letter h.

Example: 7Fh is the number 127(7\*16+15\*1) and its equivalent binary number is 01111111b.

The conversion between binary and hexadecimal is simple. To covert from hexadecimal to binary: just represent each hexadecimal digit by four binary digits: Example: 74Dh = 011101001101b

To convert from binary to hexadecimal: break the binary number into groups of four digits, and convert each group into one hexadecimal digit:

Example: 101001001110b = A4Fh

Character representation

Each character is represented by a byte or two hexadecimal digits according to ASCII code.

For example: ASCII code Letter

| 42h | В |

|-----|---|

|     |   |

|     |   |

| 5Ah | Z |

| 61h | а |

| 62h | b |

|     |   |

|     |   |

| 7Ah | z |

| 30h | 0 |

|     |   |

|     |   |

| 39h | 9 |

In assembly the ASCII representation of character can be defined by enclosing the characters in paired single (') or double (") quotes.

Example: 'A' 'e' "9"

Note 'A' = 41h, 'a' = 61h and "9" = 39h

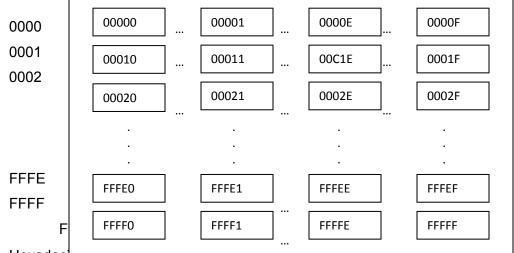

- Segment-relative addresses.

- 1) There are 16 bits in a segment register. The content of the segment register represents the paragraph number of the paragraph at which it begins.

- 2) All memory address are formed by segment-relative format which is computed as follows:

Absolute address=(segment register)\*16 + offset (16-bit) denoted by segment register: where the offset can be content of a register (16-bit) and a 16-bit value.

#### **Program stack**

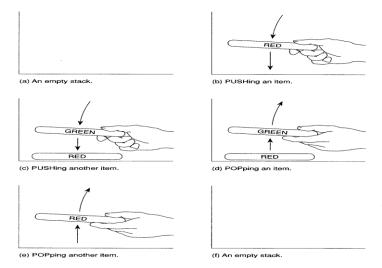

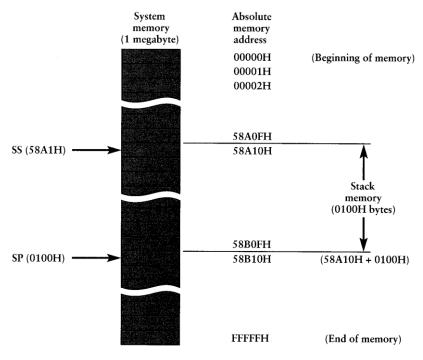

A program stack is a region of memory (RAM), which is defined by the assembly program. The program stack is implemented by setting the SS (stack segment) register and by initializing the SP (stack pointer) register to the byte immediately above the top of the sack segment. Data is moved onto the stack in word- sized units by an operation called a push and retrieved from the stack in word-sized units by an operation called pop in the reversed order (last in- first out).

Figure: Stack operations

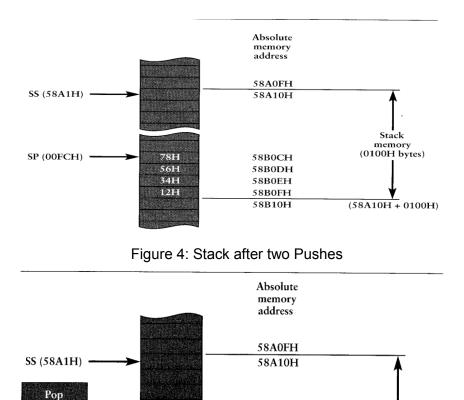

A Push operation decrements the SP register twice (-2) and put the word at SS : SP. A Pop operation retrieves the word at SS: SP and increments the SP register twice (+2) Example: A program stack is to use 100h bytes and SS= 58A1h, A = 1234h and B = 5678h. Figure 3 shows the "empty" stock, where the initial value of SP register = 100h and the stack starts at address of 58A10h and ends at address of 58B0Fh (100 bytes). Figure 4 shows the stack after two Push operations: Push A and Push B, and Figure 5 shows the stack after two Pushes and one Pop operations (Pop B).

Figure 3: Empty stack

Figure 5: Stack after two Pushes and one Pop

58B0CH

58B0DH

58B0EH

58B0FH 58B10H

78H

56H

34H

12H

Stack memory (0100H bytes)

(58A10H + 0100H)

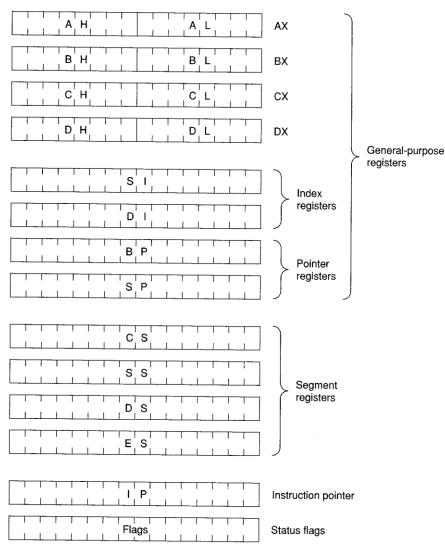

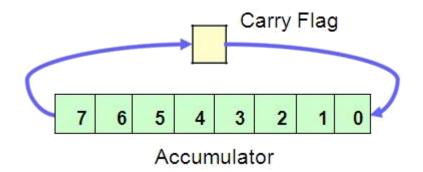

# Internal Storage (Registers)

Registers: there are 14 registers, each 16 bits (bits 0-15) in length. 14 registers are divided into five groups:

1) Four segment registers

destination

SP (00FEH)

- 2) Four data registers

- 3) Two pointer and two index registers

- 4) The instruction pointer register

- 5) The flag register (status register)

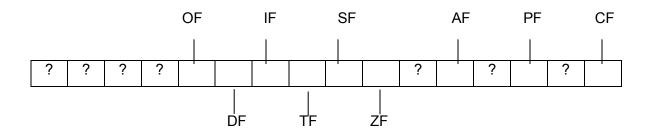

### Status register

In 8086/8088 the status register is called the flag register. The flag register contains information about the most recently executed instruction. There are 16 bits in register. But only bits 0, 2, 4 and 6-11 are used

- 1) CF (bit 0): the carry flag.

- 2) PF (bit 2): the parity flag.

- 3) AF (bit 4): the auxiliary flag.

- 4) ZF (bit 6): the zero flag.

- 5) SF (bit 7): the sign flag.

- 6) TF (bit 8): the trap flag.

- 7) IF (bit 9): the interrupt flag.

- 8) DF (bit 10): the direction flag.

- 9) OF (bit 11): the overflow flag.

Figure 6: Register Map of 8086/8088

# **Segment Registers**

The 8086/8088 has four separate "work area" for the parts of an assembly language program: data, instruction data. Each area is called a segment and has a register to associate with called segment register. Each segme 65,536 bytes, and two segments my overlap.

- 1) Data segment register (DS): indicates the beginning of the data segment.

- 2) Code segment register (CS): indicates the beginning of the code segment.

- 3) Stack segment register (SS): the stack is a part of memory. The stack is only word-addressable.

- 4) Extra data segment register (ES): points to the beginning of the extra data

# **Data Registers**

There are four 16-bit data registers that are used to store data.

1) Accumulator: AX (used for arithmetic and logic instruction).

- 2) Base register: BX (stored data)

- 3) Count register: CX (is altered by the loop instruction).

- 4) Data register: DX (used for multiply and divide instructions). An "X" register can be subdivided into a high and a low part (L, 0-7bits).

## **Pointer And Index Registers**

The segment registers point to the beginning of the various memory segments. The point registers are used to (displacements) into these segments.

- There are two pointer registers:

- 1) Stack pointer (SP)

- 2) Base pointer (BP)

- Stack pointer (SP): SP is used to hold the current stack location. SS contains the address of the begin segment and SP contains the offset.

- A stack is a pile or list of items that can be accessed one at a time and from only one end, usually the it from the top and added to the top. Thus, the stack is also called last-in first-out (LIFO) list. In8086/8 implemented by a segment of the memory, each item is a 16-bit word (2 bytes). There are two registe stack: SS and SP.

- There are two basic stack operations in 8086/8088. a. PUSH (operand) it decreases the SP by 1 wo stores a word on the stack e.g. current SP=204. AX=0010. Execution of PUSH AX will result: SP=204 0010 at memory location at address 202. b. POP (operand it removes the top word from the stack, and the bytes) to the SP.

- The base pointer (BP): BP is also can be used to point to offset within stack segment. Primarily it is used addressing modes.

- There are two index registers:

- 1) Source index register (SI)

2) Destination index register (DI) there is no significance to the words source and destination, and used interchangeably. Index registers are used in the same way subscripts that are used in hig That enable us to access the elements in an array or table.

## **Instruction Pointer**

The instruction pointer (IP) contains the offset address in the code segment of the next instruction to be execu address of the next instruction = CS : IP.

### **UNIT 2 PROGRAMMING 8085 MICROPROCESSOR**

8085 assembly language programming, addressing modes, 8085 instruction set, Instruction formats, Instruction Classification: data transfer, arithmetic operations, logical operations, branching operations, machine control —Stack and subroutines, Example Programs

### **INSTRUCTION SET OF 8085**

An instruction is a binary pattern designed inside a microprocessor to perform a specific function. The entire group of instructions that a microprocessor supports is called Instruction Set. Since the 8085 is an 8-bit device it can have up to 28 (256) instructions. However, the 8085 only uses 246 combinations that represent a total of 74 instructions. Each instruction has two parts. The first part is the task or operation to be performed. This part is called the —opcodell (operation code). The second part is the data to be operated on. This part is called the —opcodell —operandl.

### Instruction Size

• Depending on the operand type, the instruction may have different sizes. It will occupy a different number of memory bytes.

- Typically, all instructions occupy one byte only.

- The exception is any instruction that contains immediate data or a memory address.

- Instructions that include immediate data use two bytes.

- One for the opcode and the other for the 8-bit data.

- Instructions that include a memory address occupy three bytes.

- One for the opcode, and the other two for the 16-bit address.

#### **Classification of Instruction Set**

- Data Transfer Instruction

- Arithmetic Instructions

- Logical Instructions

- Branching Instructions

- Machine Control Instructions

## DATA TRANSFER INSTRUCTIONS

| Opcode | Operand | Description         |

|--------|---------|---------------------|

| MOV    | Rd, Rs  | Copy from source to |

|        | M, Rs   | destination.        |

|        | Rd, M   |                     |

|        |         |                     |

This instruction copies the contents of the source register into the destination register. The contents of the source register are not altered. If one of the operands is a memory location, its location is specified by the contents of the HL registers. Example: MOV B, C or MOV B, M.

| Opcode | Operand  | Description          |

|--------|----------|----------------------|

| MVI    | Rd, Data |                      |

|        | M, Data  | Move immediate 8-bit |

|        |          |                      |

The 8-bit data is stored in the destination register or memory. If the operand is a memory location, its location is specified by the contents of the H-L registers. Example: MVI B, 57H or MVI M, 57H.

| Opcode | Operand        | Description      |

|--------|----------------|------------------|

| LDA    | 16-bit address | Load Accumulator |

The contents of a memory location, specified by a 16- bit address in the operand, are copied to the accumulator. The contents of the source are not altered. Example: LDA 2034H

| Opcode | Operand           | Description               |

|--------|-------------------|---------------------------|

| LDAX   | B/D Register Pair | Load accumulator indirect |

The contents of the designated register pair point to a memory location. This instruction copies the contents of that memory location into the accumulator. The contents of either the register pair or the memory location are not altered. Example: LDAX B

| Opcode | Operand        | Description              |

|--------|----------------|--------------------------|

| STA    | 16-bit address | Store accumulator direct |

The contents of accumulator are copied into the memory location specified by the operand. Example: STA 2500 H

| Opcode | Operand   | Description                |

|--------|-----------|----------------------------|

| STAX   | Reg. pair | Store accumulator indirect |

The contents of accumulator are copied into the memory location specified by the contents of the register pair. Example: STAX B

| Opcode | Operand        | Description                |

|--------|----------------|----------------------------|

| SHLD   | 16-bit address | Store H-L registers direct |

The contents of register L are stored into memory location specified by the 16-bit address. The contents of register H are stored into the next memory location. Example: SHLD 2550 H

| Opcode | Operand | Description           |

|--------|---------|-----------------------|

| XCHG   | None    | Exchange H-L with D-E |

The contents of register H are exchanged with the contents of register D. The contents of register L are exchanged with the contents of register E. Example: XCHG

| Opcode | Operand | Description                                |

|--------|---------|--------------------------------------------|

| SPHL   | None    | Copy H-L pair to the Stack<br>Pointer (SP) |

This instruction loads the contents of H-L pair into SP. Example: SPHL

| Opcode | Operand | Description                    |

|--------|---------|--------------------------------|

| XTHL   | None    | Exchange H–L with top of stack |

The contents of L register are exchanged with the location pointed out by the contents of the SP. The contents of H register are exchanged with the next location (SP + 1). Example: XTHL

| Opcode | Operand | Description                               |

|--------|---------|-------------------------------------------|

| PCHL   | None    | Load program counter with<br>H-L contents |

The contents of registers H and L are copied into the program counter (PC). The contents of H are placed as the high-order byte and the contents of L as the low-order byte. Example: PCHL

| Opcode | Operand   | Description             |

|--------|-----------|-------------------------|

| PUSH   | Reg. pair | Push register pair onto |

|        |           | stack                   |

The contents of register pair are copied onto stack. SP is decremented and the contents of highorder registers (B, D, H, A) are copied into stack. SP is again decremented and the contents of low-order registers (C, E, L, Flags) are copied into stack. Example: PUSH B

| Opcode | Operand   | Description                |

|--------|-----------|----------------------------|

| POP    | Reg. pair | Pop stack to register pair |

The contents of top of stack are copied into register pair. The contents of location pointed out by SP are copied to the low-order register (C, E, L, Flags). SP is incremented and the contents of location are copied to the high-order register (B, D, H, A). Example: POP H

| Opcode | Operand            | Description                        |              |

|--------|--------------------|------------------------------------|--------------|

| OUT    | 8-bit port address | Copy<br>accumulato<br>8- bit addre | from<br>vith |

The contents of accumulator are copied into the I/O port. Example: OUT 78 H

| Opcode | Operand            | Description                                                    |

|--------|--------------------|----------------------------------------------------------------|

| IN     | 8-bit port address | Copy data to accumulator<br>from a port with 8- bit<br>address |

The contents of I/O port are copied into accumulator. Example: IN 8C H

# **1. ARITHMETIC INSTRUCTIONS**

These instructions perform arithmetic operations such as addition, subtraction, increment, and decrement.

## Addition

Any 8-bit number, or the contents of register, or the contents of memory location can be added to the contents of accumulator. The result (sum) is stored in the accumulator. No two other 8-bit registers can be added directly. Example: The contents of register B cannot be added directly to the contents of register C.

| Opcode | Operand | Description               |

|--------|---------|---------------------------|

| ADD    | R       | Add register or memory to |

|        | М       | accumulator               |

|        |         |                           |

The contents of register or memory are added to the contents of accumulator. The result is stored in accumulator. If the operand is memory location, its address is specified by H-L pair. All flags are modified to reflect the result of the addition. Example: ADD B or ADD M

| Opcode | Operand | Description               |

|--------|---------|---------------------------|

|        |         |                           |

| ADC    | R       | Add register or memory to |

|        | М       | accumulator with carry    |

|        |         |                           |

The contents of register or memory and Carry Flag (CY) are added to the contents of accumulator. The result is stored in accumulator. If the operand is memory location, its address is specified by H-L pair. All flags are modified to reflect the result of the addition. Example: ADC B or ADC M

| Opcode | Operand    | Description                  |

|--------|------------|------------------------------|

| ADI    | 8-bit data | Add immediate to accumulator |

The 8-bit data is added to the contents of accumulator. The result is stored in accumulator. All flags are modified to reflect the result of the addition. Example: ADI 45

| Н      |            |                                         |

|--------|------------|-----------------------------------------|

| Opcode | Operand    | Description                             |

| ACI    | 8-bit data | Add immediate to accumulator with carry |

The 8-bit data and the Carry Flag (CY) are added to the contents of accumulator. The result is stored in accumulator. All flags are modified to reflect the result of the addition. Example: ACI 45 H

| Opcode | Operand   | Description                   |

|--------|-----------|-------------------------------|

| DAD    | Reg. pair | Add register pair to H-L pair |

The 16-bit contents of the register pair are added to the contents of H-L pair. The result is stored in H-L pair. If the result is larger than 16 bits, then CY is set.No other flags are changed. Example: DAD B

# Subtraction

Any 8-bit number, or the contents of register, or the contents of memory location can be subtracted from the contents of accumulator. The result is stored in the accumulator. Subtraction

is performed in 2's complement form. If the result is negative, it is stored in 2's complement form. No two other 8-bit registers can be subtracted directly.

| Opcode | Operand | Description                                  |

|--------|---------|----------------------------------------------|

| SUB    | R<br>M  | Subtract register or memory from accumulator |

The contents of the register or memory location are subtracted from the contents of the accumulator. The result is stored in accumulator. If the operand is memory location, its address is specified by H-L pair. All flags are modified to reflect the result of subtraction. Example: SUB B or SUB M

| Opcode | Operand | Description                                                    |

|--------|---------|----------------------------------------------------------------|

| SBB    | R<br>M  | Subtract register or<br>memory from accumulator<br>with borrow |

The contents of the register or memory location and Borrow Flag (i.e. CY) are subtracted from the contents of the accumulator. The result is stored in accumulator. If the operand is memory location, its address is specified by H-L pair. All flags are modified to reflect the result of subtraction. Example: SBB B or SBB M

| Opcode | Operand    | Description             |

|--------|------------|-------------------------|

|        |            |                         |

| SUI    | 8-bit data | Subtract immediate from |

|        |            | accumulator             |

|        |            |                         |

The 8-bit data is subtracted from the contents of the accumulator. The result is stored in accumulator. All flags are modified to reflect the result of subtraction. Example: SUI 45 H

| Opcode | Operand    | Description             |

|--------|------------|-------------------------|

| SBI    | 8-bit data | Subtract immediate from |

|  |  | accumulator with borrow |

|--|--|-------------------------|

|--|--|-------------------------|

The 8-bit data and the Borrow Flag (i.e. CY) is subtracted from the contents of the accumulator. The result is stored in accumulator.All flags are modified to reflect the result of subtraction. Example: SBI 45 H

Increment/Decrement

The 8-bit contents of a register or a memory location can be incremented or decremented by 1. The 16-bit contents of a register pair can be incremented or decremented by 1. Increment or decrement can be performed on any register or a memory location.

| Operand | Description         |

|---------|---------------------|

|         |                     |

| R       | Incrementregisteror |

| М       | memory by 1         |

|         |                     |

|         | R                   |

The contents of register or memory location are incremented by 1. The result is stored in the same place. If the operand is a memory location, its address is specified by the contents of H-L pair. Example: INR B or INR M

| Opcode | Operand | Description                |

|--------|---------|----------------------------|

|        |         |                            |

| INX    | R       | Increment register pair by |

|        |         | 1                          |

|        |         |                            |

|        |         |                            |

The contents of register pair are incremented by 1. The result is stored in the same place. Example: INX H

| Opcode | Operand | Description           |

|--------|---------|-----------------------|

| DCR    | R       | Decrement register or |

|        | Μ       | memory by 1           |

The contents of register or memory location are decremented by 1. The result is stored in the same place. If the operand is a memory location, its address is specified by the contents of H-L pair. Example: DCR B or DCR M

| Opcode | Operand | Description                     |

|--------|---------|---------------------------------|

| DCX    | R       | Decrement register pair by<br>1 |

The contents of register pair are decremented by 1. The result is stored in the same place. Example: DCX H

# 2. LOGICAL INSTRUCTIONS

These instructions perform logical operations on data stored in registers, memory and status flags. The logical operations are:

- $\Box$  AND

- $\Box$  OR

- Rotate

- □ Compare

- □ Complement

AND, OR, XOR

Any 8-bit data, or the contents of register, or memory location can logically have

- □ AND operation

- □ OR operation

- □ XOR operation

### with the contents of accumulator. The result is stored in accumulator.

| Opcode | Operand | Description             |

|--------|---------|-------------------------|

| ANA    | R       | Logical AND register or |

|        | М       | memory with accumulator |

The contents of the accumulator are logically ANDed with the contents of register or memory. The result is placed in the accumulator. If the operand is a memory location, its address is specified by the contents of H-L pair. S, Z, P are modified to reflect the result of the operation. CY is reset and AC is set. Example: ANA B or ANA M.

| Opcode | Operand    | Description                            |

|--------|------------|----------------------------------------|

| ANI    | 8-bit data | Logical AND immediate with accumulator |

The contents of the accumulator are logically ANDed with the 8-bit data. The result is placed in the accumulator. S, Z, P are modified to reflect the result.CY is reset, AC is set. Example: ANI 86H.

| Opcode | Operand | Description                                    |

|--------|---------|------------------------------------------------|

| ORA    | R<br>M  | Logical OR register or memory with accumulator |

|        | Μ       | memory with accumulato                         |

The contents of the accumulator are logically ORed with the contents of the register or memory. The result is placed in the accumulator. If the operand is a memory location, its address is specified by the contents of H-L pair.S, Z, P are modified to reflect the result. CY and AC are reset. Example: ORA B or ORA M.

| Opcode | Operand    | Description                           |

|--------|------------|---------------------------------------|

| ORI    | 8-bit data | Logical OR immediate with accumulator |

The contents of the accumulator are logically ORed with the 8-bit data. The result is placed in the accumulator. S, Z, P are modified to reflect the result.CY and AC are reset. Example: ORI 86H.

| Opcode | Operand | Description                                     |

|--------|---------|-------------------------------------------------|

| XRA    | R<br>M  | Logical XOR register or memory with accumulator |

The contents of the accumulator are XORed with the contents of the register or memory. The result is placed in the accumulator. If the operand is a memory location, its address is specified by the contents of H-L pair. S, Z, P are modified to reflect the result of the operation. CY and AC are reset. Example: XRA B or XRA M.

| Opcode | Operand    | Description                    |

|--------|------------|--------------------------------|

| XRI    | 8-bit data | XOR immediate with accumulator |

The contents of the accumulator are XORedwith the 8-bit data. The result is placed in the accumulator. S, Z, P are modified to reflect the result. CY and AC are reset. Example: XRI 86H.

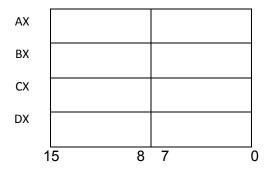

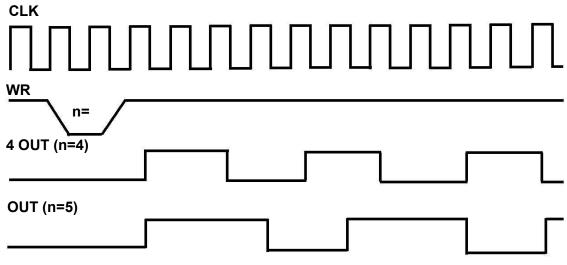

# Rotate

Each bit in the accumulator can be shifted either left or right to the next position as shown in fig5.

| Opcode                                       | Operand | Description             |  |

|----------------------------------------------|---------|-------------------------|--|

| RLC                                          | None    | Rotate accumulator left |  |

| Carry Flag<br>7 6 5 4 3 2 1 0<br>Accumulator |         |                         |  |

Fig 5. : Work flow of RLC

Each binary bit of the accumulator is rotated left by one position. Bit D7 is placed in the position of D0 as well as in the Carry flag. CY is modified according to bit D7. S, Z, P, AC are not affected. Example: RLC.

| Opcode | Operand | Description              |

|--------|---------|--------------------------|

| RRC    | None    | Rotate accumulator right |

Each binary bit of the accumulator is rotated right by one position. Bit D0 is placed in the position of D7 as well as in the Carry flag. CY is modified according to bit D0. S, Z, P, AC are not affected. Example: RRC.

| Opcode | Operand | Description                           |

|--------|---------|---------------------------------------|

| RAL    | None    | Rotate accumulator left through carry |

ig 6. : Work flow of RAL

Each binary bit of the accumulator is rotated left by one position through the Carry flag as shown in fig 6. Bit D7 is placed in the Carry flag, and the Carry flag is placed in the least significant position D0. CY is modified according to bit D7. S, Z, P, AC are not affected. Example: RAL.

| Opcode | Operand | Description                            |

|--------|---------|----------------------------------------|

| RAR    | None    | Rotate accumulator right through carry |

Each binary bit of the accumulator is rotated right by one position through the Carry flag. Bit D0 is placed in the Carry flag, and the Carry flag is placed in the most significant position D7. CY is modified according to bit D0. S, Z, P, AC are not affected. Example: RAR.

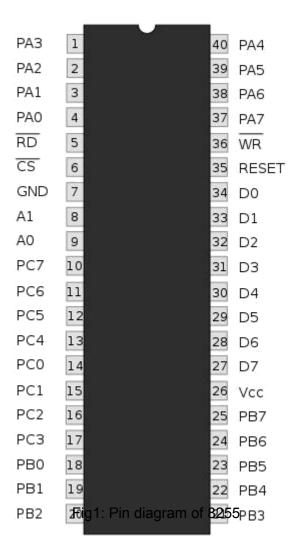

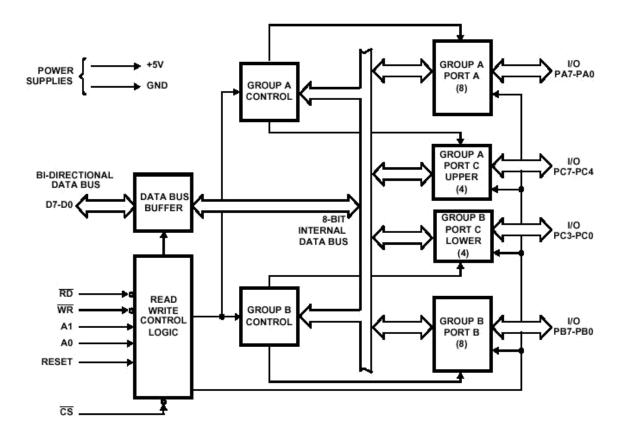

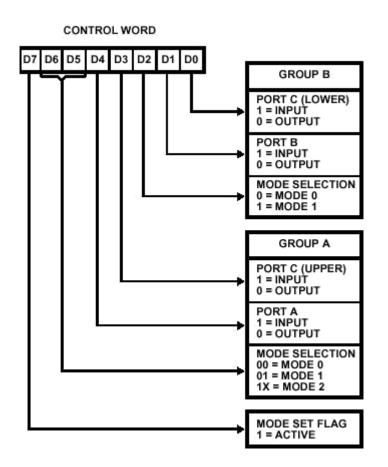

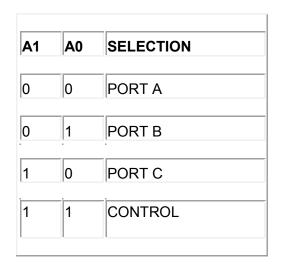

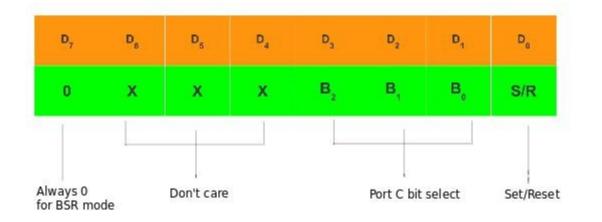

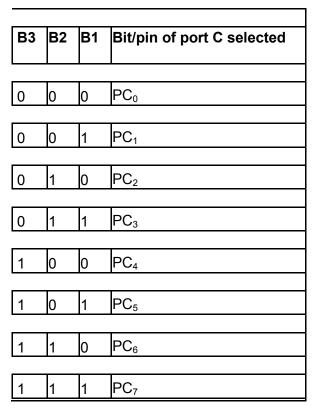

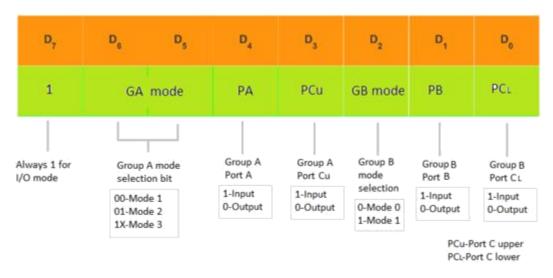

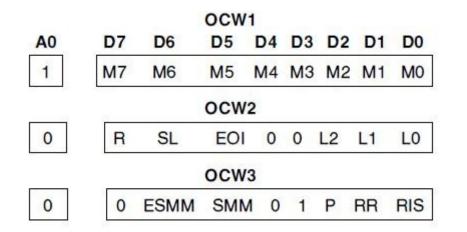

# COMPARE